OCSwifter™

特許第6310139号

低入力電流フォトカプラの高速化回路

9.6〜57.6 kbps @ If = 300 μA

2017年 10月 17日

細田 隆之

- 目次

- 概要

- 背景技術

- 汎用フォトカプラの基本的使用法 — 単純プルアップ(PU)

- 従来のフォトカプラ高速化技術の一例 — フォールディッド・カスコード(FC)

- フォトカプラの高速化 — 低遮断電圧スイッチ・カスコード(LSC)

- LSCによる高速化の結果

- フォトカプラの高速化 — バイアス付きスイッチ・カスコード(BSC)

- BSCによる高速化の結果

- フォトカプラのエミッタ出力での使用例 — エミッタ・フォロワ(EF)

- フォトカプラの高速化 — ヘテロ・ペア・スイッチ (HPS)

- HPSによる高速化の結果

- フォトカプラの高速化 — クランプ付きヘテロペア・スイッチ (CHS)

- CHSによる高速化の結果

- まとめ

- 重要な注意点

- REFERENCE

産業用機器や、組み込み機器のマイクロコントローラ等の電気的絶縁を要する箇所で、低電圧・低消費電流で動作し10kbpsを超える中速伝送レートに対応するフォトカプラが求められている。 従来のフォトトランジスタによる汎用フォトカプラでは低電圧・低消費電流では動作速度が遅くなり数kbpsを超える伝送レートを得ることは困難で、高速通信用のICフォトカプラではあまり低電圧・低消費電流では動作出来ない。 筆者は簡易な構成で、安価なフォトトランジスタによる汎用フォトカプラを低電圧・低消費電流で使用時の動作速度を数倍に向上した、フォトカプラあるいはフォトカプラ出力回路を考案した。 これは、従来のカスコード接続のように能動領域に限定するのではなく、スイッチング動作を積極的に利用することで、低消費電力と高速化を両立させている。

市販のフォトカプラではフォトトランジスタを使用した安価で伝送レートが数kbps程度までの汎用フォトカプラと、フォトダイオードとICを使用した伝送レートが1Mbpsを超える高速フォトカプラに二極化していて、それらの動作速度の間を埋める数10kbpsで低電圧・低消費電流のフォトカプラがあまり存在しない。 受光素子にフォトトランジスタを使用した汎用フォトカプラでは、フォトトランジスタの受光部のベース面積が大きいため、本質的にベース・コレクタ間容量Cobが大きく、コレクタ出力を単純プルアップで使用した場合には、オンからオフへの立ち上がり時間はプルアップ抵抗とミラー効果でCobが増大したコレクタ容量との積の時定数で決まるため、低消費電流のためにプルアップ抵抗を10kΩ以上に大きくした場合には立ち上がり時間が遅くなり、10kbpsを超えるような伝送レートで使用することが出来ない。

フォトカプラでは動作電流と伝送レートはトレードオフの関係にあり、単純プルアップでは低消費電流と高速動作は両立できない。 所望の伝送レートを得ようとすれば動作電流を増やす必用がある。 単純プルアップでの実例を下に示す。 TLP293 は汎用フォトカプラの一例として使用したもので、東芝のフォトトランジスタ出力型の汎用フォトカプラである。これは低入力電流を特徴としている。

fig.1 単純プルアップでの過渡応答特性例 fig.2 フォトカプラの単純プルアップの回路例 (RL=4.7kΩ)

Vdd=1.8V, If=303uA, (Ic=380uA), 10kbps

tf=26.55us, tr=27.58us, (td=18.976us)fig.3 単純プルアップでの過渡応答特性例 fig.4 フォトカプラの単純プルアップの回路例 (RL=15kΩ)

Vdd=3.3V, If=340uA, (Ic=220uA), 9.6kbps

tf=14.34us, tr=76.99us, td=56.10us

●その他 TLP293 単純プルアップ出力の測定回路例と特性例

フォトカプラの動作速度を改善する従来の技術には、ショットキー・クランプやベースバイアス、トランジスタをカスコード接続してフォトトランジスタを能動領域で使用するもの等がある。 従来の技術は何れも、動作速度向上を目的として少数キャリアの蓄積時間の低減やCobあるいはミラー効果の低減に主眼を置いたものであった。 fig.6 に汎用フォトカプラをフォールディッド・カスコードにより高速動作を図った例を示す。やや複雑な回路と数mAの動作電流で100kbps程度の伝送速度が得られているものの、 高速通信用フォトカプラに対して特に有利な点があるわけではない。

fig.5 FCの過渡応答特性例 fig.6 FCの回路例

Vcc=5.0V, If=1.59mA, 115.2kbps, (Ic=CTR*If≃2mA)

tf=660ns, tr=870ns, td=1.80us

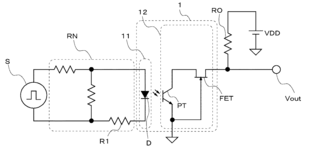

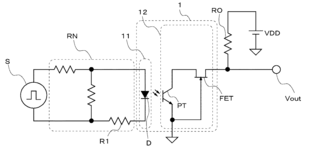

筆者は、低電流動作時あるいはコレクタ抵抗が比較的大きい場合の伝送レートは、主にオンからオフへの立ち上がり時間によって制限されている点に着目し、受光素子であるフォトトランジスタがオンからオフに立ち上がり始めた時点でフォトトランジスタのコレクタ出力をコレクタ出力とプルアップ抵抗の間に挿入したアナログスイッチで切り離せば、アナログスイッチの容量とプルアップ抵抗との時定数で決まる速度にまで、立ち上がり時間が低減できることを見出した。

このアナログスイッチとして、カットオフ電圧が -0.3V 前後と小さく、かつドレイン遮断電流がプルアップ抵抗と電源電圧で決まる電流に対して十分大きな、ディプリーション・モードのFETを使用すれば、特段の制御回路を設けることなくフォトトランジスタのコレクタ出力をコレクタ出力がオンからオフに立ち上がり始めた時点で切り離すことができかつ、LVCMOSのような低電圧ロジックICにもそのまま接続することが出来る。この手段を使用した構成例を fig.8 に示す。以降簡便のため、この構成例をLSC(Low cut-off voltage Switch Cascode)と称す。 併せてフォトトランジスタのコレクタ電圧はコレクタ電流にかかわらずカットオフ電圧から0Vの範囲になるため、フォトトランジスタのコレクタから見て低抵抗となり、フォトトランジスタが飽和状態からの回復時には、カスコード接続と同様にミラー容量の低減効果が得られる。

この手段はフォトトランジスタを能動領域で使用することで高速化を図るのではなく、アナログスイッチを用いて切り離すことにより高速化を図る点で、従来のバイポーラ・トランジスタのカスコード接続とは本質的に異なるものである。

fig.7 LSCの過渡応答特性例 fig.8 LSCの回路例

Vdd=3.3V, If=350uA, 9.6kbps, (Ic=220uA)

tf=5.12us, tr=32.13us, td=19.54us

●その他 TLP293 LSC応用回路例と特性例

fig.7 中 REF2 は fig.3 の単純プルアップ(RL=15kΩ)の場合の波形である。 入力電流と負荷抵抗が同条件の単純プルアップに比べて、立ち下がり時間で約 2.8倍 (14.34us/5.12us≒2.8)、立ち上がり時間で約 2.5倍 (76.99us/32.13≒2.49) の高速化が得られている。 単純プルアップでは使用限界であった 9.6kbpsの伝送レートに対して、19.2kbpsでの伝送が可能になっている。

LSCのFETのソースにカットオフ電圧をやや超える電圧のバイアスを加えてやることにより、FETスイッチがオフになるのを早めることができる。 この手段を使用した構成例を fig.10 に示す。以降簡便のため、この構成例をBSC(Biased Switch Cascode)と称す。 fig.10 において、D1はシリコン・ダイオードであるが、D1はダイオードに限らず、バイアス電圧を決定するためのFETのソース・ゲートに対しての並列素子であればよく、 ツェナー・ダイオード、TVS、LEDあるいはバンドギャップ・リファレンス等の定電圧回路でもよい。

fig.9 BSCの過渡応答特性例 fig.10 BSCの回路例

Vdd=3.3V, If=303uA, 19.2kbps, (Ic≤250uA)

tf=3.52us, tr=9.90us, td=12.76us

●その他 TLP293 BSC応用回路例と特性例

fig.9 中 REF2 は コレクタ・エミッタ間電圧Vce(=ゲート・ソース間電圧Vgs)の波形である。 入力電流と負荷抵抗が同条件の単純プルアップに比べて、立ち下がり時間で約 3.9倍 (14.34us/3.52us≒3.93)、立ち上がり時間で約 7.8倍 (76.99us/9.90≒7.78) の高速化が得られている。 単純プルアップでは使用限界であった 9.6kbpsの伝送レートに対して、38.4kbpsでの伝送が可能になっている。

汎用フォトカプラをエミッタフォロワ構成の能動領域で使用してやると、fig.11 に示すように低入力電流でも 10kbpsを超える伝送レートに応答する。 だがエミッタから取り出せる振幅は、入力電流If×電流伝達比CTR×プルダウン抵抗Reで決まるため、あまり大きくとれない。 ここで、プルダウン抵抗を大きな値とすると、フォトトランジスタの動作電流が小さくなって動作速度が遅くなり fig.13 に示すように応答速度が低下する。

fig.11 単純エミッタ出力の過渡応答特性例 fig.12 単純エミッタ出力の回路例 (Re=1.5kΩ)

Vdd=1.8V, If=303uA, (Ie=367uA), 10kbps

tf=14.34us, tr=15.34us, td=6.80usfig.13 単純エミッタ出力の過渡応答特性例 fig.14 単純エミッタ出力の回路例 (Re=22kΩ)

Vdd=1.8V, If=311uA, (Ie=24.5uA), 2kbps

tf=114.75us, tr=13.41us, td=80.35us

●その他 TLP293 単純エミッタ出力の測定回路例と特性例

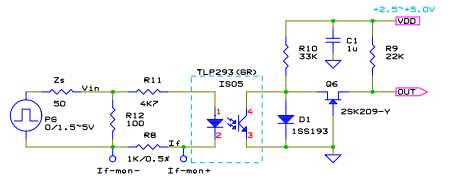

振幅は小さくても比較的高速に応答する fig.11 のエミッタ出力をBSCにおけるのバイアス回路の如くFETスイッチのソースに接続してやることにより、 高速応答で大振幅の出力を得ることが出来る。

この手段は従来のフォトトランジスタのコレクタのミラー効果をカスコード接続によって低減することで高速化を図るのではなく、 コレクタ・エミッタ間電圧がほとんど変わらずにエミッタ電流が変化して高速に動作する、電流モードでフォトトランジスタを用い、 電流帰還バイアスで動作してるFETのドレイン抵抗に対して電流を注入することによりFETのゲート・ソース間電圧を制御し、 遮断電圧の前後の小さな電圧の変化でドレイン電流をオン・オフすることによってドレイン出力電圧を変化させるという手法で高速化を図っている。

FETはフォトトランジスタからみてゲート接地で動作することになるため、FETの入力と出力は同相であるためミラー効果の影響を受けない。また、FETは多数キャリアで動作する素子であるため、バイポーラ・トランジスタにおける少数キャリアの蓄積による遅延も生じない。

この手段を使用した構成例を fig.16 に示す。 以降簡便のため、この手段を、差動増幅器の別称ロングテイルドペアに倣ってHPS(Hetero short-tailed Pair Switch)と称す。

この手段ではフォトトランジスタのエミッタと低遮断電圧のFETのソースが接続されることにより構成される疑似差動型電流スイッチを構成していて、 従来のフォトトランジスタのコレクタと出力トランジスタのエミッタあるいはソースが接続される形式のカスコード接続、あるいはフォールディッド・カスコード接続とは本質的に異なるものである。

fig.18 は fig.16 の構成例に FET のソース電位が上昇しすぎないように電圧クランプ素子(ダイオード等)を追加したものである。 このクランプ素子によりフォトトランジスタのコレクタ・エミッタ間電位が小さくなりすぎて動作速度が低下するのを防ぐ効果と、エミッタ電位の立ち下がり時間の増加を抑え、ひいては出力の立ち下がり時間の増加を抑える効果がある。

fig.15 HPSでの過渡応答特性例 fig.16 HPSの回路例

Vdd=1.8V, If=303uA, 10kbps, (Ie+Id=507uA)

tf=4.36us, tr=3.39us, td=9.90us

●その他 TLP293 HPSの測定回路例と特性例

fig.15 中 REF2 は fig.1 の単純プルアップ(RL=4.7kΩ)の場合の波形である。 入力電流と負荷抵抗が同条件の単純プルアップに比べて、立ち上がり時間で約 8.1倍 (27.58us/3.39us≒8.14)、立ち下がり時間で約 6.1倍 (26.55us/4.36us≒6.09) の高速化が得られている。 単純プルアップでは使用限界であった 9.6kbps の伝送レートに対して、38.4kbpsでの伝送が可能になっている。

但し、PC/HSTPSは、1.8〜3.3Vといった低電圧で動作するLVCMOSロジックに接続して使用できる、低電流動作で20kbps程度の中速度のデジタル伝送への適用を目的としている。 出力電流シンク能力がFETのIdssで制限されるため比較的少なくなり、トランジスタのFETが直列接続されるためにローレベルも比較的大きくなるため、旧来のTTLには適合性が良くない。 FETのピンチオフ電圧やフォトカプラのCTRのばらつきや変動により、抵抗等の最適な定数は異なることに留意する必要がある。

HPSでは、フォトカプラがオンの時のゲート・ソース間電位Vgsは、入力電流If×電流伝達比CTR×ソース抵抗Rsで決まるため、 IFやCTRが大きすぎる場合には、フォトトランジスタのコレクタ・エミッタ間電圧が下がって応答速度が遅くなったり、あるいは、 フォトカプラがオフになるときにエミッタ、ソースのノードの容量に蓄積された電荷がRsにより放電されてFETのソース電位が自己バイアス電位に落ち着くまでに余計に時間が必要となるため、 フォトトランジスタのオフから出力の立ち下がりまでの時間が遅くなることがある。

そこで、BSCにおけるバイアス回路における並列素子のように、ゲート・ソース間電圧をカットオフ電圧をやや超える電圧に制限する素子を設けることすれば、この問題を解決することが出来る。 この手段を使用した構成例を fig.18 に示す。以降簡便のため、この構成例をCHS(Clumped Hetero pair Switch)と称す。

fig.17 CHSでの過渡応答特性例 fig.18 CHSの回路例

Vdd=1.8V, If=303uA, 20kbps, (Ie+Id=507uA)

tf=4.17us, tr=3.39us, td=7.20us

REF2: Vs(max)=510mV, Vs(min)=140mVfig.19 CHSでの過渡応答特性例 fig.20 CHSの回路例

Vdd=1.8V, If=311uA, 57.6kbps

tf=4.23us, tr=3.45us, td=7.36us

●その他 TLP293 CHSの測定回路例と特性例

fig.17 中 REF2 は fig.18 の Q6 のソース電位 Vs である。フォトトランジスタがオンのときに電圧クランプダイオードによりFETのソース電位が上昇しすぎないので、立ち下がり遅延とそのジッターが電圧制限を行わないときに比べて低減されている。 クランプを行わない場合の使用限界は 38.4kbps であったが、クランプを行った結果 57.6kbps での伝送が可能になっているて、fig.1 の単純プルアップでの伝送速度に対して 6倍の伝送速度が得られている。

上に述べた、LSC、BSC、HPS、CHSの手段および測定例により簡易な構成で、安価なフォトトランジスタタイプの汎用フォトカプラを低電圧・低消費電流で用いる場合の動作速度を数倍に改善することの出来ることが示された。 これらの手段は何れもゲートが接地されたFETをスイッチとして利用しているため、これらを総称してGGFS(Grounded Gate FET Switch)出力型フォトカプラと呼ぶことにする。

ご提供携帯:弊社では、この特許の実装の実施許諾契約、並びに応用技術のコンサルティングをご提供させて頂いております。

お気軽にメールにてお問い合わせ下さい。

特許広報 特許第6310139号 — フォトカプラの出力回路及びフォトカプラ [Download 3MB pdf]

![[Mail]](/~lyuka/images/mail.gif)

© 2000 Takayuki HOSODA.

© 2000 Takayuki HOSODA.