Takayuki HOSODA

Rev.0.3 (Nov. 6, 2021)

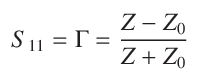

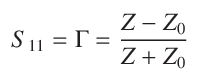

信号電力の伝送において、終端 (termination) とは、 伝送線路インピーダンス Z0 と受信端あるいは送信端のインピーダンス Z を合わせることを意味します。 Z → Z0 のとき反射係数 Γ → 0 となり、無反射となります。この状態を整合している (matched) と言います。 インピーダンスを目的のインピーダンスの合わせる、多くの場合整合状態にする、ことをインピーダンス・マッチング (impedance matching) あるいは単に、マッチングと呼びます。

直列終端 (series termination) とは送信端のインピーダンスを線路インピーダンスに整合させることを指します。 受信端が MOSFET の入力のような線路インピーダンスに比べて高いインピーダンスの場合には、 開放端反射 (open-end reflection) のような大きな反射が発生します。 この反射を送信側の終端抵抗で終端することにより反射を止め (terminate) るのことを直列終端と呼び、 その目的で送信端に直列に挿入される抵抗のことを直列終端抵抗と呼びます。

巷でよく見聞きする「高速ロジックはリンギング (ringing) が発生する」といった話ですが、 それはプロービングやバイパス・キャパシタが間違っているのでなければ、 多くの場合、終端が不適切もしくは欠如しているために多重反射が見えているのです。目安として、配線距離が tr または tf の短い方の時間の間に基板上を伝搬する距離の 1/10 を超えたら終端が必須となります。

例えば tr = 6 ns で基板上の伝搬速度が 200 mm/ns であれば、配線長が 120 mm 辺りから終端が必須となります。

シミュレーション回路

- R1005M は 1005M サイズのチップ抵抗の簡略モデルです。

- Rs が 40 mΩ というのはジャンパ抵抗を想定しています。

- 伝送線路 U1, U2, U3 は、 伝送線路インピーダンス Z0 = 80 Ω の損失のあるマイクロストリップラインを想定しています。

(e.g. 誘電体厚 h = 0.2 mm, 比誘電率 εr = 4.1, 線路幅 w = 150 μm, 導体厚 t = 18 μm → Z0 = 80 Ω)

- U1, U2, U3 の線路長 Len はそれぞれ 100, 400, 2000 [mm] で、速度係数 Vr ≃ 0.6 でモデリングしています。

Download lvc-termination.asc, the schematic file for the LTspice XVII.

シミュレーション結果

Transient response (Rs=40 mΩ)

Transient response (Rs=39 Ω)

- 直列終端抵抗がほとんど無い状態で、100 mm の伝送線路の受信端 (f1) では多重反射により大きなリンギングが発生しています。

- 20 ns のパルス幅で伝送線路長が 2 m になると、受信端 (f3) ではっきりと開放端反射が見えるようになっています。

- 伝送遅延がパルス幅と同程度の場合には、受信側の信号レベルがロジック IC のスレッショルド付近に留まる時間が長くなります。

これは誤作動やメタステーブルの原因になる場合があります。

- 伝送線路長が長い場合には伝送線路がアンテナとなって大きな不要輻射を発生することになります。

Transient response (Rs=68 Ω)

- 直列終端抵抗が伝送線路インピーダンスの半分程度の 39 Ω でも 100 mm 程度の比較的短距離ではリンギングは大分改善されています。

これは多重反射が短時間で起こるために反射エネルギーが速やかに消費されるからです。

- 反射は直列終端抵抗のインピーダンスとロジック IC の出力インピーダンスの和で終端されるため、再反射は半分より少なくなっています。

Transient response (Rs=150 Ω)

- ロジック IC の出力インピーダンス Ro と 直列終端抵抗 Rs のインピーダンスの和が 線路インピーダンス Z0 に近くなるように選ぶと、 再反射は小さなものとなります。

- 直列終端抵抗が伝送線路のインピーダンスより高い場合は開放端反射的になって同相で反射するため悪影響が大きいです。

- 伝送線路帳が短い場合でも鈍った波形となります。

- 20 ns のパルス幅で伝送線路長が 2 m になると、送信端 (n3) ではっきりと開放端反射が見えるようになっています。

- 伝送遅延がパルス幅と同程度の場合には、受信側の信号レベルがロジック IC のスレッショルド付近に留まる時間が長くなり酷く歪みます。

これは誤作動やメタステーブルの原因になる場合があります。

- 反射電力がなかなか消費されないため多重反射が長引いて誤作動的にも不要輻射的にも良くありません。

- 伝送線路長が長い場合には伝送線路がアンテナとなって大きな不要輻射を発生することになります。

直列終端の抵抗値

このシミュレーションで使用している LVC14A の出力インピーダンス Ro は 11 Ω 辺りですが、 実際の CMOS ロジック IC では、出力能力や電源電圧や温度で変わるため、ある Z0 における Rs の最適値はそれぞれに異なるものとなります。 不明の場合には次善の策として CMOS IC の出力抵抗 Ro を その定格出力電流 Io からRo ≃ 0.4 V / (1.5 Io)程度と概算して、 Rs ≤ Z0 - Ro を直列終端抵抗の値として選んでおきます。

計算例: Z0 = 80 Ω, Ro ≃ 0.4 V / (1.5 × 24 mA) ≃ 11.1 Ω → Rs = 68 Ω⚠️ このとき、Rs を大きくしすぎてはいけません。 Rs 小さい場合には、再反射の電圧は反転する方向に発生して、 それが受信端の CMOS IC に伝わり、その電圧が大きい場合には IC 内の入力保護ダイオードでクランプされるため、 ロジック・レベル的な問題にはなりにくいです。 しかし、Rs が大きい場合には再反射の電圧は反転しないため、 受信端に伝わるとロジックレベルの閾値に近くなりノイズ・マージンが減少するからです。 また、受信側のインピーダンスが低めの場合や線路の損失が大きい場合には受信信号の減衰量が増えるため、 これもまたノイズ・マージンを低下させることになります。

チップ・フェライトが回路の随所に使われているのを見ることがあります。 電源ラインにチップ・フェライトを使用するのは多くの場合正しいことですが、 EMC (Electro Magnetic Compatibility) 対策と称して、 直列終端抵抗の代わりにチップ・フェライトを入れてあるのを見かけることがありますが、 これは正しいことでしょうか。 直列終端というのは、伝送線路の負荷側から反射した電力を信号源側で終端するものです。 電力を消費するのは抵抗分だけで、リアクタンスではありません。 この電力を消費すべき箇所にリアクタンス分を持つチップ・フェライトを入れるということは、直列終端が出来なくなることを意味します。

チップ・フェライトは低周波的に見れば周波数特性があって損失のあるインダクタです。 しかし、高周波的に見れば透磁率の大きな磁性体が装荷された、表皮効果等による損失のある伝送線路です。 特性の違う2の伝送線路をつないだ場合にはその境界で必ず反射が発生することになります。 終端の観点から見ると、チップ・フェライトは事態を複雑化させて終端困難にする素子とも言えます。 終端、すなわち反射電力を消費してしまうには、負荷側か信号源側、あるいは両方でインピーダンスが伝送線路の特性インピーダンスと整合している必要がありますが、 LV-CMOS 入力のような伝送線路インピーダンスよりも遥かに高いインピーダンスの負荷に対しては、 信号源側で終端する必要があるのに、信号源側にチップ・フェライトが入っているとそこでまた反射が起きてしまうからです。

シミュレーション回路

- U4, U6 : MMZ0603S800C は TDK の 0603M サイズのチップ・フェライト の TDK による高精度モデルです。

100 MHz におけるインピーダンスが線路インピーダンス Z0 に近い値で高周波でインピーダンスが上がり過ぎないものを選んでいます。- R0603M は 0603M サイズのチップ抵抗の簡略モデルです。

- 伝送線路 U1, U2, U3 は、 伝送線路インピーダンス Z0 = 100 Ω の損失のあるマイクロストリップラインを想定しています。

(e.g. 誘電体厚 h = 0.2 mm, 比誘電率 εr = 3.5, 線路幅 w = 100 μm, 導体厚 t = 18 μm → Z0 = 100 Ω)

- U1, U2, U3 の線路長 Len は 400 [mm] で、速度係数 Vr ≃ 0.65 でモデリングしています。

- C9 の値は、Z0 と C9 で決まるカットオフ周波数が、fclk の 5 倍程度となるように選んでいます。

Download lvc-ferrite.asc, the schematic file for the LTspice XVII.

シミュレーション結果

Transient response (Len = 400 mm)

- 直列終端抵抗の代わりにチップ・フェライトだけを用いた場合、信号の受信端 (f1) では反射がなかなか減衰せずにパルス波形が大きく崩れています。

- 直列終端抵抗の代わりにチップ・フェライトを用い、受信端 (f2) に線路インピーダンスの約2倍の並列終端抵抗を追加した場合、反射は比較的速やかに減衰しています。

- 直列終端抵抗を用い、受信端 (f3) に負荷容量 C9 を僅かに追加した場合、反射は速やかに減少し、適度に帯域の制限された波形となっています。

周波数解析結果

FFT results (Len = 400 mm)

- 受信端 (f1) では fclk の基本波辺りに盛り上がりがあり、反射により振幅が増大しているのが見て取れます。

- 受信端 (f2) では並列終端により、振幅が減少しているのが見て取れます。

- 受信端 (f3) では クロック周波数 fclk の 10 倍以上を帯域外として考えてみると、 500 MHz 以上の帯域外において振幅が大きく減少しているのが見て取れます。 これは C9 の ESL L3 とあわせて帯域外に伝送ゼロ点のある LPF を形成しているからです。

これらのシミュレーションでは、正しく設計された素子値の直列終端抵抗を使用することが、高速デジタル信号の伝送において重要であることが確認できました。 EMC の観点からは、帯域外の信号レベルは直列終端+小さな負荷容量の組み合わせの方が、 チップ・フェライトを使用した場合よりも下げられて優位性があることがわかりました。

![[Mail]](/~lyuka/images/mail.gif)

© 2000 Takayuki HOSODA.

© 2000 Takayuki HOSODA.