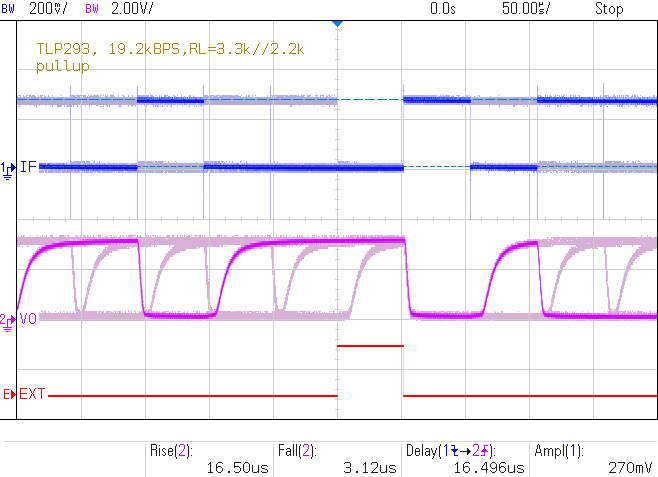

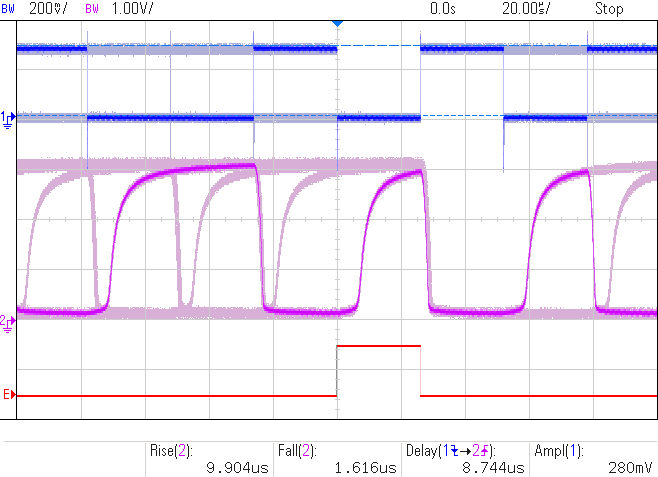

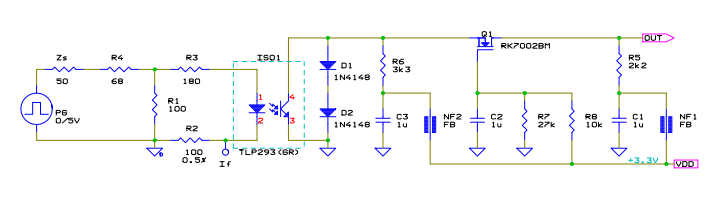

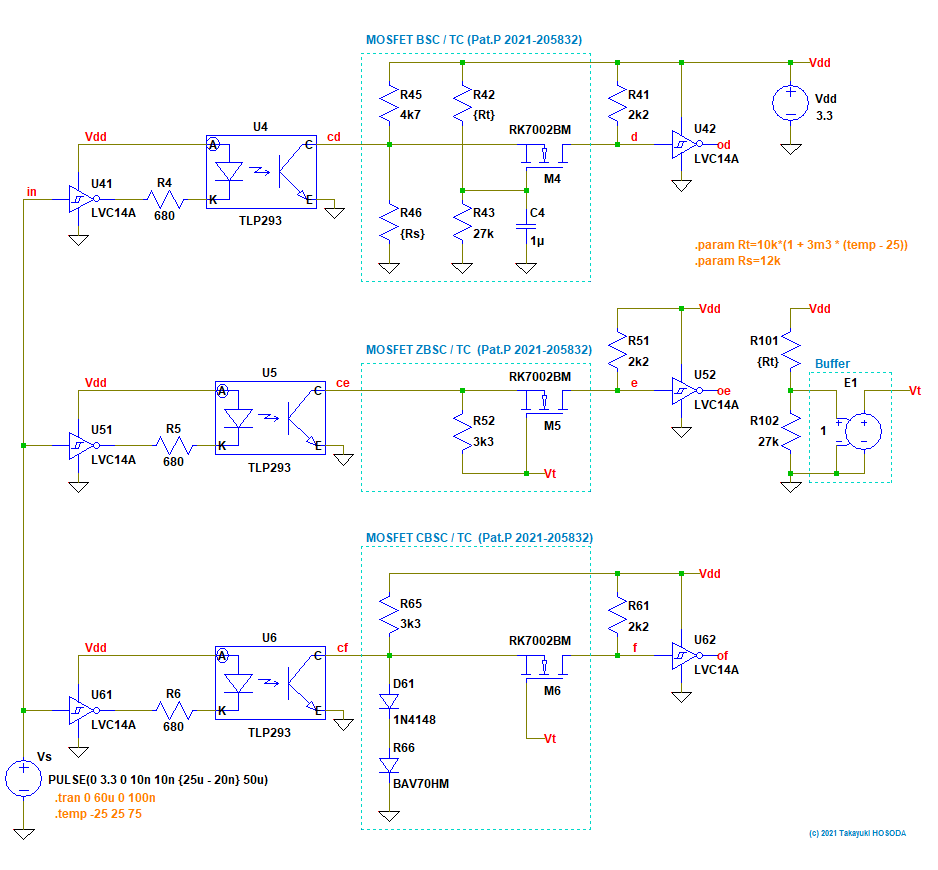

丂偙偺俰俥俤俿傪巊偭偨俴俽俠峔惉偺夞楬偱偼掅揹埑偱僗僀僢僠摦嶌偝偣傞偨傔偵僇僢僩僆僼揹埑偑亅侽丏俀乣亅侽丏俆倁掱搙偺丄

傾僫儘僌僗僀僢僠梡偺俰俥俤俿傪巊梡偟偰偄傞偑丄偦偆偄偭偨俰俥俤俿偺揱払僐儞僟僋僞儞僗俧倣偼廫暘偵戝偒偔偼側偔丄

椺偊偽俇侽倣俽掱搙偱偁傞丅傑偨丄僆儞偺偲偒偵棳偣傞僪儗僀儞揹棳俬倓傕廫暘偵偼戝偒偔側偄丅

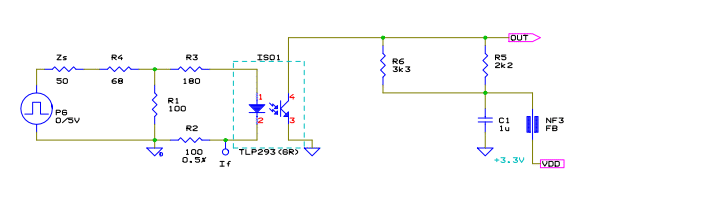

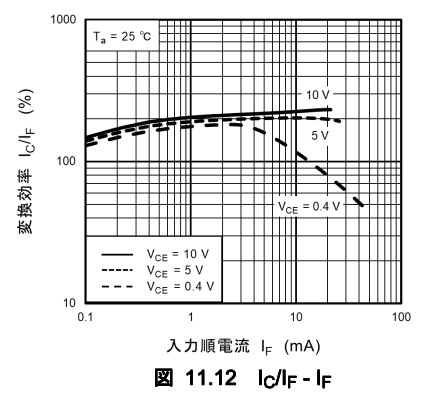

丂僼僅僩僇僾儔偺僼僅僩僩儔儞僕僗僞偑僆儞偺偲偒偺弌椡朞榓揹埑乮昗弨乯傪俀侽侽倣倁

乮俬們亖俀侽侽兪俙乯 偲偡傞偲丄偡側傢偪俰俥俤俿偺僎乕僩丒僜乕僗娫揹埑倁倗倱亖亅

俀侽侽倣倁偲側傞丅偙偺偲偒丄僆儞帪偺弌椡偺掅儗儀儖揹埑傪儘僕僢僋俬俠摍偺掅儗儀儖

擖椡揹埑倁俬俴偵懳偟偰廫暘掅偄揹埑丄椺偊偽俿俿俴偺掅儗儀儖弌椡揹埑憡摉偺係侽侽倣

倁埲壓偵偡傞偨傔偵偼俰俥俤俿偺僪儗僀儞僜乕僗娫揹埑倁倓倱偑俀侽侽倣倁埲壓偱偁傞昁

梫偑偁傞丅偙偺忦審傪枮偨偡偨傔偵嫋梕偱偒傞僆儞帪偺僪儗僀儞揹棳俬倓丵倧値偼椺偊偽

侾倣俙埲壓偱偁傞丅

丂俰俥俤俿偺僪儗僀儞揹棳俬倓丵倧値偺忋尷偼丄儘僕僢僋儗儀儖傪妋曐偡傞偨傔偵昁梫側

僾儖傾僢僾掞峈偺掞峈抣傪婯掕偡傞丅忋婰偺椺偱偼僪儗僀儞揹棳俬倓丵倧値偼侾倣俙埲壓

偵惂尷偝傟傞偨傔丄椺偊偽揹尮揹埑偑俁丏俁倁偱偁傞応崌偵偼丄僾儖傾僢僾掞峈偲偟偰偼

俁丏俁倁乛侾倣俙亖俁丏俁倠兌埲忋偺抣偺傕偺傪巊梡偡傞昁梫偑偁偭偨丅

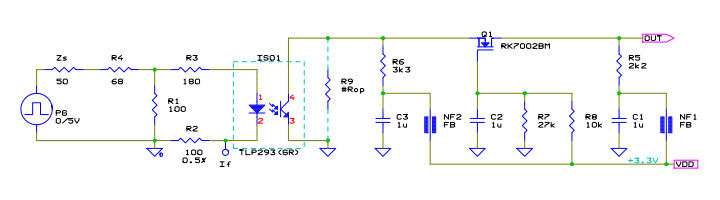

丂偙偺傗傗崅傔偺僾儖傾僢僾掞峈偺抣偼丄掅徚旓揹棳梡偱俋俇侽侽倐倫倱偲偄偭偨斾妑揑

掅偄揱憲懍搙偺応崌偵偼栤戣偵偼側傜側偄偑丄徚旓揹棳傪婔暘憹傗偟偰崅懍壔傪恾傠偆偲

偟偨応崌偵偼崅懍壔偺朩偘偲側偭偰偄偨丅

丂傑偨丄俰俥俤俿偺僺儞僠僆僼揹埑偼侾侽侽亷偲偄偭偨崅壏偱偼戝偒偔晧懁偵偢傟傞偨傔丄

俰俥俤俿偑僼僅僩僩儔儞僕僗僞偺僐儗僋僞傪愗傝棧偡偨傔偺僗僀僢僠偲偟偰偺摦嶌偑巒傑傞僐儗僋僞揹埑偑忋徃偡傞丅

偙傟偵敽偄丄弌椡偑僆僼偵側傞帪娫偑挿偔側傝丄僷儖僗揱憲偺僷儖僗暆榗偑憹戝偡傞偲偄偆栤戣傕偁偭偨丅

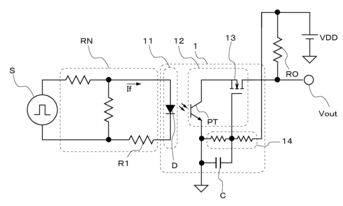

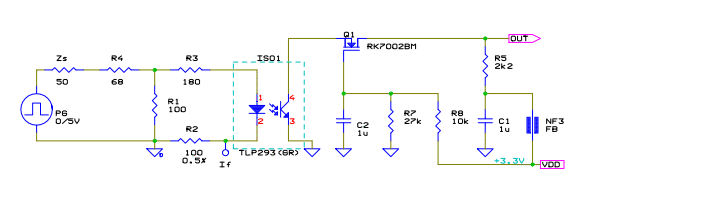

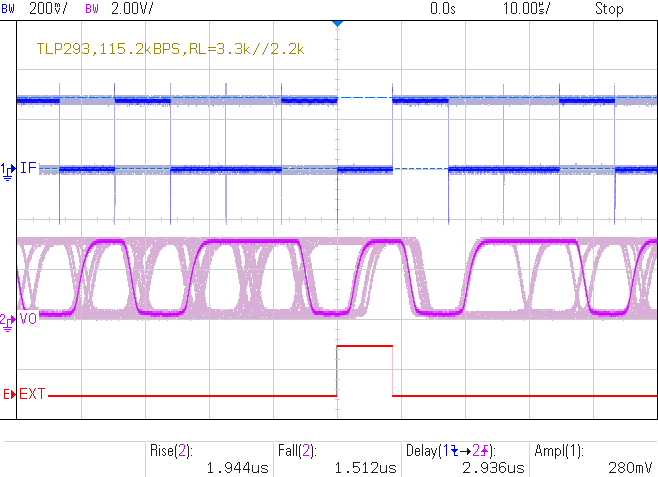

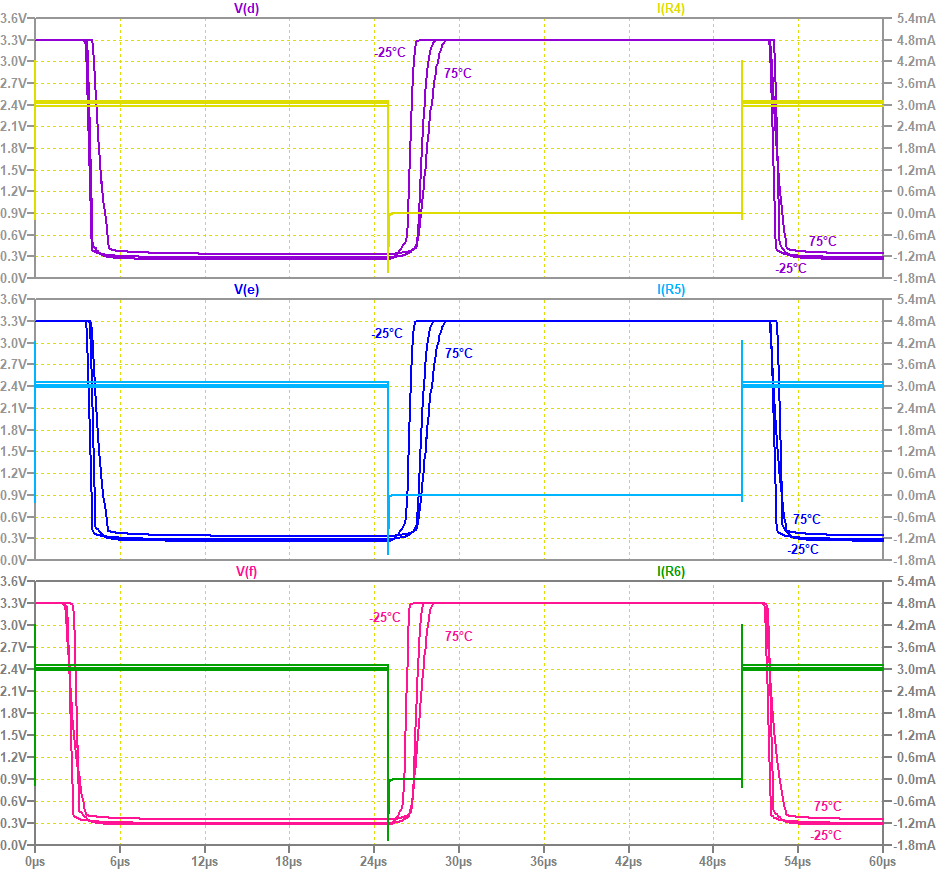

丂傑偨僼僅僩僩儔儞僕僗僞偺僐儗僋僞傪僾儖傾僢僾掞峈傪夘偟偰揹尮偵愙懕偡傞廬棃偺峔

惉偵偍偄偰丄僾儖傾僢僾掞峈偺抣傪彫偝偔偟偰僼僅僩僇僾儔偺崅懍壔傪恾偭偨応崌偵偼丄

摦嶌揹棳偺戝偒偝偲敪擬偵婲場偟丄僼僅僩僇僾儔偺揹棳曄姺斾俠俿俼偺掅壓丄弌椡僼僅僩

僩儔儞僕僗僞傪朞榓椞堟偱巊梡偡傞応崌偺俠俿俼偺掅壓丄宱擭曄壔偵傛傞俠俿俼偺掅壓偺

壛懍偵傛傞怣棅惈偺掅壓傗屘忈棪偺憹壛偲偄偭偨栤戣偑偁偭偨丅

丂忋婰偺栤戣偵娪傒丄杮敪柧偺栚揑偼丄拞掱搙偺擖椡揹棳偱巊梡偡傞拞崅懍僨僕僞儖怣崋

揱憲偵揔偟偨僼僅僩僇僾儔傪採嫙偡傞偙偲偱偁傞丅

![[Mail]](/~lyuka/images/mail.gif)

© 2000 Takayuki HOSODA.

© 2000 Takayuki HOSODA.