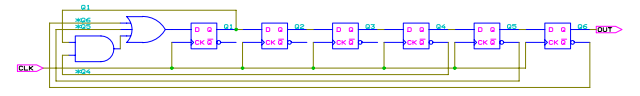

fig.1 6-5 ジョンソン カウンタ

フリーランで動作するジョンソンカウンタは fig.1 のように論理回路を初段への帰還部に入れるだけで構成できる。●帰還部の論理式

fig.1 6-5 ジョンソン カウンタ

ハードウェア記述言語でMNジョンソンカウンタを記述するときの帰還部の最小構成の論理式を tbl.1 に示す。

tbl.1 最小構成のMN ジョンソン カウンタの帰還部の論理式

M N 帰還部 1 1 D1 = !Q1 2 1 D1 = !Q2 # !Q1 2 2 D1 = !Q2 3 1 D1 = !Q3 # !Q2 # !Q0 3 2 D1 = !Q3 # !Q2 3 3 D1 = !Q3 # !Q2 & Q1 4 1 D1 = !Q4 # !Q3 # !Q2 # !Q1 4 2 D1 = !Q4 # !Q3 # !Q2 4 3 D1 = !Q4 # !Q3 4 4 D1 = !Q4 # !Q3 & Q1 5 1 D1 = !Q5 # !Q4 # !Q3 # !Q2 # !Q1 5 2 D1 = !Q5 # !Q4 # !Q3 # !Q2 5 3 D1 = !Q5 # !Q4 # !Q3 5 4 D1 = !Q5 # !Q4 # !Q3 & Q1 5 5 D1 = !Q5 # !Q4 & Q1 6 1 D1 = !Q6 # !Q5 # !Q4 # !Q3 # !Q2 # !Q1 6 2 D1 = !Q6 # !Q5 # !Q4 # !Q2 6 3 D1 = !Q6 # !Q5 # !Q4 # !Q3 6 4 D1 = !Q6 # !Q5 # !Q4 # !Q3 # !Q2 # !Q1 6 5 D1 = !Q6 # !Q5 # !Q4 & Q1 6 6 D1 = !Q6 # (!Q5 # !Q4) & Q1 7 1 D1 = !Q7 # !Q6 # !Q5 # !Q4 # !Q3 # !Q2 # !Q1 7 2 D1 = !Q7 # !Q6 # !Q5 # !Q4 # !Q3 # !Q2 7 3 D1 = !Q7 # !Q6 # !Q5 # !Q4 # !Q3 7 4 D1 = !Q7 # !Q6 # !Q5 # !Q4 7 5 D1 = !Q7 # !Q6 # !Q5 # !Q4 & Q1 7 6 D1 = !Q7 # !Q6 # !Q5 & Q1 7 7 D1 = !Q7 # (!Q6 # !Q5) & Q1 8 1 D1 = !Q8 # !Q7 # !Q6 # !Q5 # !Q4 # !Q3 # !Q2 # !Q1 8 2 D1 = !Q8 # !Q7 # !Q6 # !Q5 # !Q4 # !Q2 8 3 D1 = !Q8 # !Q7 # !Q6 # !Q5 # !Q3 8 4 D1 = !Q8 # !Q7 # !Q6 # !Q5 # !Q4 8 5 D1 = !Q8 # !Q7 # !Q6 # !Q5 8 6 D1 = !Q8 # !Q7 # !Q6 # !Q5 & Q1 8 7 D1 = !Q8 # !Q7 # !Q6 & Q1 8 8 D1 = !Q8 # (!Q7 # !Q6) & Q1

![[Mail]](/~lyuka/images/mail.gif)

© 2000 Takayuki HOSODA.

© 2000 Takayuki HOSODA.