⚠️ Demo の実行には Java 8 のインストール と 例外サイトへの追加 が必要です。

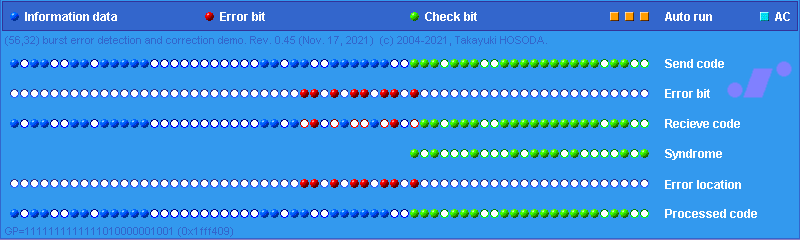

この符号は (72, 48) バースト誤り訂正符号を 16-bit 短縮した符号で、バースト長が 12 までのバースト誤りの訂正が可能です。

ライガーの限界 (Reiger Bound) を達成している最適バースト誤り訂正符号 (Optimas burst-error-correcting code) の一つです。

その生成多項式 (generator polynomial) の一つは、式 (1) で表されます。GP(x) = x24 + x23 + x22 + x21 + x20 + x19 + x18 + x17 + x16 + x15 + x14 + x13 + x12 + x10 + x3 + 1 … (1)生成多項式の係数 (coefficients) 表記では、2進数 (16進数) で 1 1111 1111 1111 0100 0000 1001 ( 0x1fff409 ) と表されます。

この生成多項式は 嵩忠雄氏によって見つけ出された[3]もので、 SSR mode-S Acquisition squitter 等で使われています。

情報ビット長や符号長、バースト訂正能力などが全て 8 の倍数なので色々と好都合です。

全ビットが '1' になった誤りも検出できます。

⚠️ Demo の実行には Java 8 のインストール と 例外サイトへの追加 が必要です。

- 符号理論, 今井秀樹, 電子情報通信学会, ISBN4-88552-090-8

- T.Kasami, "Optimum shortened cyclic codes for burst-error correction", IEEE Trans. Inform. Theory, vol.IT-9, no.2, pp.105-109, 1963/04.

- T.Kasami, S.Matoba, "Some efficient shortened cyclic codes for burst-error correction", IEEE Trans. Inform. Theory, vol.IT-10, no.3, pp.252-253, 1964/07.

2元 BCH 符号及びバースト誤り訂正符号

![[Mail]](/~lyuka/images/mail.gif)

© 2000 Takayuki HOSODA.

© 2000 Takayuki HOSODA.