デジタル同期検波器では、数値的周波数変換器の数値的局部発振器に用いられる数値制御発振器(NCO)の信号のスプリアスが、 イメージ妨害や微小な信号を検波する場合に検知レベルの下限を決める重要な要素になっている。 この発明では、前述のスプリアスが数値制御発振器(NCO)の量子化誤差の周期性に起因することに鑑み、 NCOの波形分割数を素数とすることでそのスプリアスを効果的に抑圧することが出来るようになった。

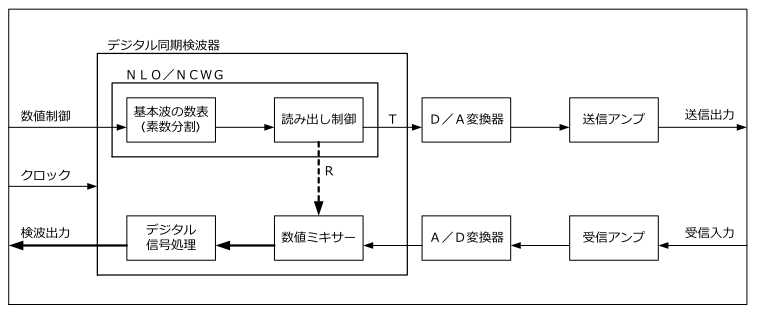

図1 デジタル同期検波器のブロック図

デジタル同期検波器では、数値的周波数変換器の数値的局部発振器に用いられる数値制御発振器(NCO)の信号のスプリアスが、 イメージ妨害や微小な信号を検波する場合に検知レベルの下限を決める重要な要素になっている。 この発明では、前述のスプリアスが数値制御発振器(NCO)の量子化誤差の周期性に起因することに鑑み、 NCOの波形分割数を素数とすることでそのスプリアスを効果的に抑圧することが出来るようになった。

図1 デジタル同期検波器のブロック図

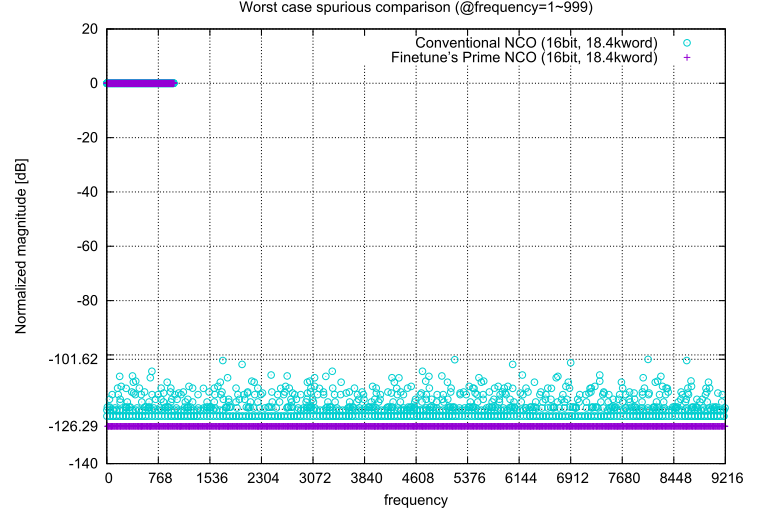

図2 スプリアスの改善例

本発明は、数値制御波形発生器(以下、「NCWG」と呼ぶ)に関し、特に、送受信信号を離散的数値のデジタル信号で扱う同期検波器(以下、「デジタル同期検波器」と呼ぶ)の、数値的局部発振器(以下、「NLO」と呼ぶ)として用いるNCWG及びデジタル同期検波器に関する。●背景技術

●発明が解決しようとする課題デジタル同期検波機では、数値的周波数変換器(以下、「数値ミキサー」と呼ぶ)のNLOに用いられるNCWGの信号のスプリアスが、イメージ妨害や微小な信号を検波する場合に信号検知レベルの下限を決める重要な要素となっている。 従来より、NCWGとしては、数値的な帰還による数値的な発振回路によって正弦波や、それに直交する余弦波を同時に生成したりするもの(以下、「NCO」と呼ぶ)(例えば特許文献1参照)や、基本波の波形を数表(ルックアップテーブル)として作成しておき、生成する周波数に応じて読み出し方を変えるものがある(例えば特許文献2参照)。

特許文献1に記載のNCOでは、誤差の蓄積や安定度の点から、出力として必要とする以上の数値分解能が必要である。このため、NCOでは、発生させる周波数によりスプリアスの発生具合が変動する。よって、NCOは、簡易なデジタル通信などには適しているものの、微小な受信信号の変化を検知するような目的(以下、「微弱信号検知」と呼ぶ)には余り適していない。 一方、特許文献2に記載のNCWGでは、出力として必要とするビット数が決まれば、全ての発生させうる信号について数表により一意に定まるため、スプリアスの予測が可能で微弱信号検知に適している。

【特許文献1】特開平9-135364号公報

【特許文献2】特開2000-252750号公報

●課題を解決するための手段しかしながら、NCWGにより単一、又は複数の周波数の信号を発生させる場合、単一の正弦波、又は複数の正弦波を適当な位相と振幅で加算した波形を生成しようとしても、量子化誤差のために目的の周波数以外の信号、即ちスプリアスが発生すること自体を避けることはできない。 この量子化誤差に起因するスプリアスを低減するには、一義的には量子化ビット数を増やし、又は併せてサンプリングレートを増大させる必要があるが、どちらも物理的な制約を受ける。

ここで、NCWGにより発生させる波形が、上記の正弦波のように一周期の間に絶対値が同じ振幅値を周期的に通る波形において、基本波の数表を用いてその整数倍周波数の波形を生成する場合に、生成する波形の基本波に対する倍数と数表の波形分割数が小さな整数比(以下単に、「小さな整数比」と略す)になるときは、量子化誤差が基本波の整数倍の頻度で周期発生することになる。

図3 従来のNCWGによる8倍波形と、その量子化誤差

図3は、波形分割数N=256、フルスケールFS=±4095である13ビット×256ワードの正弦基本波の数表を持つ従来のNCWG(図中 NCWG-B) の、生成する波形の基本波に対する倍数で表した周波数(以下、「freq」と略す)がfreq=8での量子化誤差を示すタイミングチャートである。 図4は、当該量子化誤差に起因するスプリアスの実例を示すプロットである。

図4 2種類のNCWGの8倍周波数波での量子化誤差に起因するスプリアスの実例

図3及び図4の従来のNCWGはいずれも、freq=8でNの256に対して1:32の「小さな整数比」になっている場合の例である。 図3では「小さな整数比」になっているため、量子化誤差に顕著な周期性が発生しているのが見て取れ、この状態では、特定の周波数で大きなスプリアスを発生する事となる。

図4の従来のNCWG(図中 NCWG-B) では量子化誤差の顕著な周期性による、特定の周波数における大きなスプリアスが見て取れる。 この状態でのスプリアスの最大値は-85.516dBで、そうでない場合であるNCWG-Pの-92.055dBに比べ6.539dB大きく、4dB以上、言い換えれば電力比で倍以上悪くなっている。

デジタル同期検波器において、NLOの波形が、図4に示すような特定の周波数において大きなスプリアスが発生する図3のような波形となった場合、その特定の周波数に雑音や妨害波があった場合には数値ミキサーの後の検波波形に妨害となって現れ、これは正規の受信信号と区別することができないため、この妨害を検波後に除去することは出来ない。 このような状況では、検波器の性能が大きく劣化することとなる。

図4の従来のNCWGの場合では、スプリアスの最大値が、13ビットの数表のダイナミックレンジによる基準値-20log(2^13-1)≒-78.3dBに対して-85.5dBであり、基準値の-7.2dBに留まってしまっているのが分かる。 図3に例を示したような、特に、半導体メモリーの容量や読み出しのためのカウンターの都合上頻繁に用いられる、2のべき乗を波形分割数としたNCWGでは、この周期的誤差によるスプリアスの発生が顕著であり、性能の潜在的な弱点となっている。

●発明の効果本発明者は、発明が解決しようとする課題に述べたスプリアスが、数表のから生成する波形の量子化誤差の周期性に起因することに鑑み、数表の波形分割数が生成する波形の周期の小さな整数比とならない値にすれば、特定の周波数におけるスプリアスの発生が抑圧されることを見出し、本発明を完成するに至った。 特に数表の波形分割数を素数とした場合には、数表の基本波形自体に含まれる周期性以外には周期性を持たなくなるため、周期性に起因するスプリアスの発生が効果的に抑圧できる。

図4では、本発明に係るNCWG-Pで発生するスプリアスは、8倍周波数波において、8周期毎でしか周期性を持たないことから特定の周波数にスプリアスが集中せず、従来のNCWGに比べ、6.5dB以上少なくなっている。 フルスケールを16ビットに拡張したものや、波形分割数が何万というものでも、スプリアスの発生機構は変わらないため、波形分割数Nを素数とした場合には、波形分割数が例えば2の冪や小さな素数の積のものに比べて、発生するスプリアスの最大値が小さくなっている。

本発明に伴って行った多くのシミュレーション結果により、波形分割数が例えば2の冪や小さな素数の積のものに比べ、波形分割数を素数とすることにより、発生するスプリアスの最大値がおよそ6dB低減するという知見が得られている。

●適用分野(実例、及び案)本発明によれば、簡易な構成でスプリアスの発生を効果的に抑圧する数値制御波形発生器及びデジタル同期検波器を提供することができる。

ご提供形態:弊社では、この特許の実装の実施許諾契約並びに応用技術のコンサルティングをご提供させて頂いております。

お気軽にメールにてお問い合わせ下さい。

![[Mail]](/~lyuka/images/mail.gif)

© 2000 Takayuki HOSODA.

© 2000 Takayuki HOSODA.